Peer-to-peer, engineer-to-engineer questions and answers from the EDABoard.com engineering community around analog ICs and analog design. Click the “Read more” link and follow the entire conversation and maybe add your two cents by logging in to EDAboard.com.

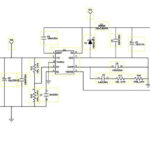

Transformerless power supply help – I use this power supply for a small product where the load is only 50mA at 5V. Without load voltage is around 5.6V and with load 4.8V. The circuit works fine only one problem happens each time. The Zener diode. Zener diode damages frequently especially when a spike comes. How can I improve this circuit so that Zener diode becomes stable? Read more

Voltage level shifting – I am using a dual supply opamp -5v and +5v and I require the output to swing between 0v to 5v, whilst the input swings between -5v to +5v. I usually work with opamps with inputs between 0v to 5v, but the +/- input has confused me. Read more

Basic question about Johnson noise – Is the noise for 2 parallel resistors equal or less than their parallel equivalent? Or to put some numbers Vnoise (2Meg || 2Meg) vs Vn(1Meg). Read more

Derivation of closed-loop transfer function – I am reading on the section on derivation of closed-loop transfer function of the type-II PLL I found that expression (9.14) is not the differentiated version. It should have the apostrophe ( ‘ or ‘) character to imply that it is the result of differentiating Eq. (9.13) with respect to time. In this case, I really suspect if expression (9.15) is correct or not since H(S) = (9.14) * (Kvco / s) / (1 + (9.14) * (Kvco / s) Could anyone suggest if I overlook something? Read more

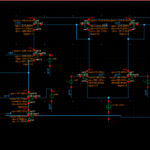

Non-overlapping clocks with a “envelope clock” – I am trying to design 8 phases non-overlapping clocks with a pair of non-overlapping “envelope clocks” as depicted in the picture below. Unlike the non-overlapping-ness is secured by the topology, the phase relationship between the 2 envelope signals and 8 phases clock is affected by process variations. In other words, one of the envelope signal may fail to cover the last clock phase or may cover the first clock phase of the next 8 phases round. Is there a topology that I can use to secure the phase relationship between the 2 envelope signals and 8 phases clock as I desired? Read more

RL circuit simulation problems in Proteus – I simulate simple RL circuit in Proteus but it gives wrong values, values different from the theoretical calculation. The voltage across inductor when the switch is open should be 110 v but proteus give 5V but using PSpice it gives result near the theoretical result. Read more

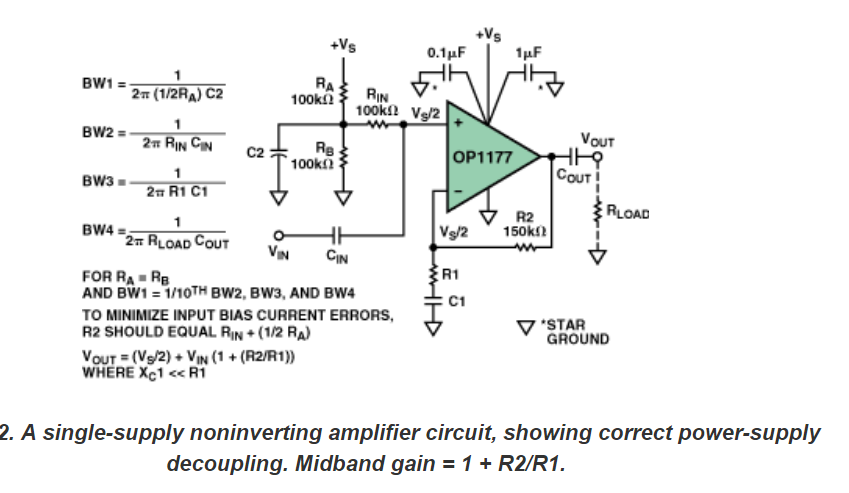

Star ground single supply op amp – I was going through a design recommendation and came across this Star Ground concept. Why is the +Vs has bypass capacitors connected to star ground? Is it this ground same as actual ground. Also, the Vs/2 voltage shown at negative input of op amp has to be connected physically to the resistor divider network or will it automatically appear that point. Read more

Fast switch circuit for -30V – I am trying to build a switch circuit to switch up to -30Volts and to supply up to 5Amp. I need to generate a -30V test pulse for 100usec. So the output should be either open or a 100usec, pulse. I have transient pulse generator, but those generate either -30V or Zero voltage. I don’t want that. I want either nothing or -30V. Read more

Get exact position of motor – In a system motor is connected to gear and its interconnected to other gear. Gear ratio is 7.5. To complete 360 degrees the motor need 7.5 rotations. I need to detect the exact position of the motor even when power fails. Read more

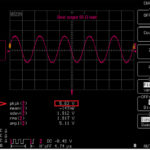

Diff pair power supply rejection ratio – I run the PSRR simulation for current source load diff amp and active current source load diff am and the PSRR plots are different and these differences are conditioned by the diode connection. Read more