Cadence Design Systems, Inc. announced that its custom and analog/mixed-signal (AMS) IC design tools have achieved certification for Samsung Foundry’s 7nm Low Power Plus (7LPP) process technology. This certification ensures Cadence and Samsung Foundry mutual customers of a highly automated circuit design, layout, signoff and verification flow with full extreme ultraviolet lithography (EUV) support. This certification complements the earlier announced certification of the Cadence full-flow digital and signoff tools on Samsung 7LPP process technology.

Cadence Design Systems, Inc. announced that its custom and analog/mixed-signal (AMS) IC design tools have achieved certification for Samsung Foundry’s 7nm Low Power Plus (7LPP) process technology. This certification ensures Cadence and Samsung Foundry mutual customers of a highly automated circuit design, layout, signoff and verification flow with full extreme ultraviolet lithography (EUV) support. This certification complements the earlier announced certification of the Cadence full-flow digital and signoff tools on Samsung 7LPP process technology.

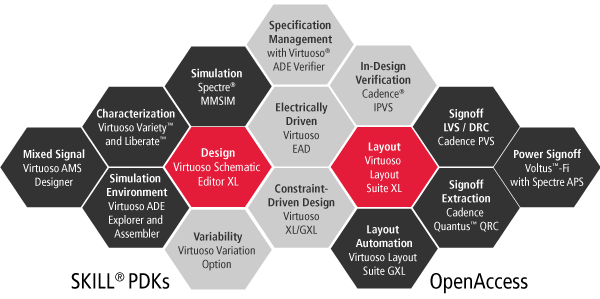

The Cadence custom and AMS flow includes the Virtuoso Analog Design Environment (ADE), Virtuoso Schematic Editor, Virtuoso Layout Suite with its Advanced-Node Platform, Virtuoso Space-Based Router, Spectre Circuit Simulator, Voltus-Fi Custom Power Integrity Solution, Quantus Extraction Solution, Physical Verification System, Litho Physical Analyzer, Cadence CMP Predictor and LDE Electrical Analyzer. These tools can be used throughout the complete custom AMS flow, including:

- Front-end design: Corner, statistical, and reliability simulation; circuit and device checks; layout-dependent effect (LDE) analysis, and simulation and verification management.

- Custom layout design: An advanced, electro-migration and parasitic-aware environment that includes device and module generation, automated placement and routing, layout editing, and dynamic DRC checking with Virtuoso Integrated PVS DRC, interactive PVS metal fill, in-design DFM flows for LDE, process hotspot repair (PHR), pattern analysis and optimization, and chemical mechanical polishing (CMP) check, as well as support for correct-by-design multiple patterning flow.

- Post-layout parasitic simulation and IR drop (IREM) analysis and integrated signoff: Including parasitic extraction, design rule checks, layout versus schematic checks, dummy metal fill and programmable electrical rule checks (PERC).

- AMS design: Digital standard cell placement, pin optimization and automated space-based routing.