New semiconductor devices created with the Internet of Things in mind will be a hot topic at the 61st annual IEEE International Electron Devices Meeting (IEDM) taking place at the Washington D.C. Hilton Hotel from December 7-9, 2015. Considered a premier forum for scientists and engineers in the field of micro and nanoelectronics, IEDM this year includes several presentations oriented toward energy efficient devices catering to the needs of low-power electronics.

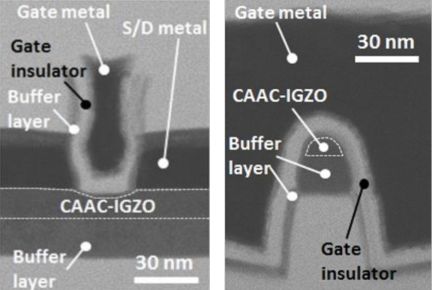

One such presentation covers high-frequency, low-leakage indium-gallium-zinc-oxide (IGZO) transistors. A team from Japan’s Semiconductor Energy Laboratory Co. will describe how they made 20-nm gate-all-around MOSFETs with super low off-state currents of < 0.1 pA, yet with cutoff frequencies exceeding 10 GHz. The transistors were made from thin films of IGZO. They were built using a self-aligned process that eliminated overlaps from the gate to the source and drain, rendering the channel immune from short-channel effects that otherwise would degrade performance. Integrated in a DRAM memory cell to demonstrate performance, their extremely low off-current allowed for data retention exceeding ten days at 125°C. The paper, 20-nm-node Trench-Gate-Self-Aligned Crystalline In-Ga-Zn-Oxide FET with High Frequency and Low Off-State Current; is by Daisuke Matsubayashi et al, Semiconductor Energy Laboratory Co., LTD.

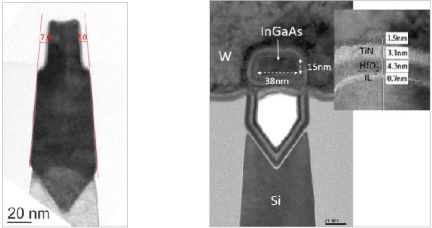

Another paper covers InGaAs nanowire FETs on silicon. Though III-V channels have benefits for low-power logic devices, there are have been questions about their manufacturability. At IEDM, a team led by Imec will discuss gate-all-around, high-performance InGaAs nanowire MOSFETs built on 300-mm silicon wafers. They have a high transconductance (gm = 2,200) that indicates despite having a lattice-mismatched substrate, the InGaAs channel material maintains its high carrier velocity. The paper, Gate-All-Around InGaAs Nanowire FETS with Peak Transconductance of 2200 μS/μm at 50nm Lg Using a Replacement Fin RMG Flow, is by N. Waldron et al, Imec/ASM.

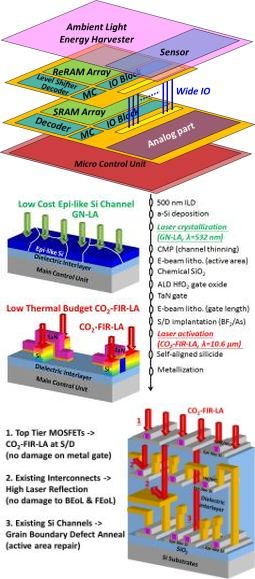

A point of emphasis at IEDM is that of integrating chip electronics and sensors on the same substrate to make IoT sensors that can be super-inexpensive. In that regard, a team led by Taiwan’s National Nano Device Laboratories investigated a way of improving the design of monolithic 3D chips. The normal way of constructing 3D circuits is by stacking separate chips and connecting them electrically with through-silicon vias (TSVs). But TSVs have significant disadvantages including relatively narrow I/O bandwidth. 3D ICs that are monolithic have no TSVs but their construction entails thermal annealing that can damage transistors — each layer in a 3D device must be annealed to remove stresses in its crystalline silicon structure, and also to activate the dopants which have been implanted in it.

The researchers addressed this issue by using a CO2 far-infrared laser at 400°C to selectively pulse-anneal specific areas of the silicon (the source-drain regions). They used this technique to build a sub-40-nm monolithic IC containing a variety of heterogeneous functions—logic, SRAM, RRAM, sense and analog amplifiers, and gas sensors. No device degradation was reported, and the researchers say their technique is suitable for making the low-power, low-cost, small-footprint and heterogeneously integrated devices needed for the Internet of Things.

The paper, Low-Cost and TSV-free Monolithic 3D-IC with Heterogeneous Integration of Logic, Memory and Sensor Analogy Circuitry for Internet of Things, is by Tsung-Ta Wu et al, National Nano Device Laboratories/National Tsing Hua University.

For registration and other information, visit the IEDM 2015 home page www.ieee-iedm.org, or contact Phyllis Mahoney, conference manager telephone (301) 527-0900 ext. 2.