(editor’s note: Intrigued by the problem? Have a question or optional solution? Then click the “Read more” link and follow the conversation on EDAboard.com or log in to EDAboard and participate in the analog IC forum thread.)

Noise figure vs 1-dB point of LNA – If the low noise amplifier (or power amplifier) operates in saturation region or beyond its 1 dB compression point, then how will the noise figure of the amplifier will be affected? Read more

Spectrum analyzer input impedance questions- This spectrum analyzer has a 50R input resistor. I wonder, why is it needed? The input filter is designed for 50R but why is the resistor needed? Also, I have designed a 50R step attenuator that will be placed at the input of the spectrum analyzer. Do I need to include the 50R resistor and where? Read more

Analog filter delay time – I am trying to design an analog low pass filter. I was wondering if there is any equation showing the relation between the filter spec and order of the filter, and its settling time and propagation delay. And if there is any, will it depend on the filter topology? Read more

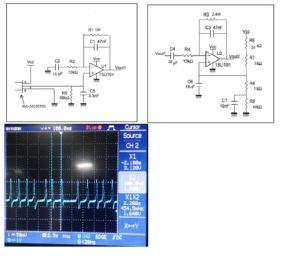

PIR .5Hz noise seen in 2nd stage output amplifier – I’m trying to design a PIR that has a range of 10m. When I probe the output of the second stage amplifier, a noise with 0.5Hz is seen which is causing false detection. I’ve tried to reduce the range to 5m but the noise presence is still there. Ijust removed the PIR and checked the output it was clean. Read more

Does higher Q factor lead to higher resonance frequency? – Do you want resonance frequency as high as possible — which means higher bandwith? What happen if you operate the system at resonance frequency? Or higher than resonance frequency? Read more

Drain capacitance of donut transistor – I’ve read that because the drain area of the donut transistor is shared by the gates on all four sides, the parasitic drain capacitance is reduced to minimum. Why would the drain area surrounded by the gate have a minimum drain capacitance? Read more

Stb and AC analysis don’t match – This is the first time I’m designing a differential amplifier on Cadence (an amplifier for a neural probe) and after doing a stability analysis something strange happened: The loop gain doesn’t correspond to the gain I obtained when doing an AC analysis (the one I desired) and I truly don’t understand why. Read more

What causes LDO output ripples? – I would like to understand what is causing the LDO output to have ripples when there is current load switching? In my simulation test bench, I’m just placing an ideal current load to switch from 0mA to 30mA periodically and load cap about 100pF connected to the output of the LDO. There is an output ripple about 200mVpp whenever the current is switching. Read more

Reconfigurable antenna isolating the bias from the RF signal? – I am working on a pattern reconfigurable antenna and I need to bias the PIN diode from a battery through a bias line. For this, I need an RF choke inductance to isolate the AC from the bias line. Is there any specific formula to select the RF choke to select for a frequency band of 1.8 to 3 GHZ? Read more

Over-current protection for 12V DC to 220V DC commercial Chinese inverters – I’ve fixed many of the commercial Chinese inverters. I know that the LM324 compactor is the one responsible for all sorts of protections in these units. Overvoltage also can be easily detected with the same method “voltage divider”. However, I can’t see the notorious current sense resistor in any of the primary FETs. Read more